C'è una sola risposta corretta per ogni domanda

Usare lo spazio bianco sul retro del foglio per appunti, se serve

1) Si vuole implementare uno spazio di memoria di 16Mx8bit usando due moduli RAM da 8Mx8bit, in modo che il modulo 1 dia corpo alle celle di indirizzo *pari* ed il modulo 2 a quelle di indirizzo *dispari*. I select dei due moduli /s1, /s2 vengono generati da maschere che hanno come ingressi:

- a) a23\_a1

- b) a0

- c) a23

- d) Nessuna delle precedenti

2) Un D-latch viene pilotato con la sequenza di ingressi  $\{d,c\} = \{0,0\}, \{1,0\}, \{0,1\}, \{1,0\}$ . Alla fine, la sua uscita:

- a) Vale 1

- b) Vale 0

- c) Dipende dal valore impostato al reset

- d) Nessuna delle precedenti

$$T \geq T_{\text{prop}} + T_{\text{a valle}}$$

3) La disuguaglianza scritta sopra riguarda:

- a) Il percorso da registro a registro in una rete di Mealy Ritardato

- b) Il percorso da registro a registro in una rete di Moore

- c) Il percorso da registro a uscita in una rete di Mealy

- d) Nessuna delle precedenti

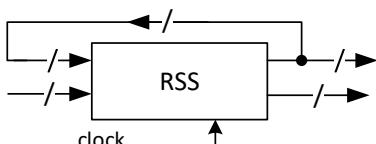

4) L'uscita del circuito in figura può evolversi in modo non prevedibile se la RSS è una rete di:

- a) Moore

- b) Mealy

- c) Mealy ritardato

- d) Nessuna delle precedenti

S0: **begin** ...; STAR<=MJR; **end**

S1: **begin** ...; STAR<=S0; **end**

| St. int. | $\mu$ -code | Ceff | $\mu$ -add T | $\mu$ -add F | $\mu$ -tipo |

|----------|-------------|------|--------------|--------------|-------------|

| S0       | ...         |      |              |              |             |

| S1       | ...         |      |              |              |             |

5) Data la porzione di descrizione e lo schema di ROM riportati sopra, come vanno riempite le quattro colonne di ROM evidenziate a destra?

a)

|   |   |   |   |

|---|---|---|---|

| - | - | - | 1 |

| - | - | - | 0 |

b)

|   |    |    |   |

|---|----|----|---|

| - | -  | -  | 1 |

| - | S0 | S0 | 0 |

c)

|     |    |   |   |

|-----|----|---|---|

| MJR | -  | - | 1 |

| 0   | S0 | - | 0 |

d) Nessuna delle precedenti

```

input a0, a1;

...

casex(STAR)

S0: begin ...; STAR<=(a1,a0)==`B00)?S1:S0; end

S1: begin ...; STAR<=(a1,a0)==`B11)?S0:S1; end

endcase

```

6) Per sintetizzare secondo il modello PO/PC la descrizione sopra riportata, quante uscite ha la rete combinatoria di condizionamento?

- a) 1

- b) 2

- c) Non è possibile stabilirlo

- d) Nessuna delle precedenti

7) Si supponga di voler aggiungere al processore visto a lezione l'istruzione PUSHB indirizzo. Quanti byte verranno letti in memoria in totale durante la fase di fetch?

- a) 7

- b) 5

- c) 4

- d) Nessuna delle precedenti

8) Nel calcolatore visto a lezione, per generare una tensione analogica:

- a) si esegue una OUT ad un opportuno offset

- b) si manda in esecuzione un sottoprogramma che fa ciclare il processore in attesa attiva

- c) si esegue una IN da un opportuno offset

- d) Nessuna delle precedenti

9) Chi scrive nei flag FI ed FO di un'interfaccia con handshake?

- a) Il processore

- b) L'interfaccia

- c) I dispositivi esterni

- d) Nessuna delle precedenti

10) Il numero di bit utili da trasmettere in una singola trasmissione seriale ha un limite superiore dovuto a:

- a) l'overhead dei bit di start e di stop

- b) il fatto che la linea di trasmissione non è un conduttore ideale

- c) l'imprecisione relativa dei clock di trasmettitore e ricevitore.

- d) Nessuna delle precedenti

Cognome e nome: \_\_\_\_\_

Matricola: \_\_\_\_\_

Link al form Google per le risposte (i due link sono equivalenti):

<https://forms.gle/Kr3W3EDx5mPnHAfx6>

<https://tinyurl.com/bdhand6t>

♥ - cuori

Barrare una sola risposta per domanda

Il punteggio finale è  $-1 \times (n. \text{ di risposte errate} + n. \text{ domande lasciate in bianco})$

Usare lo spazio bianco sul retro del foglio per appunti, se serve

1) Si vuole implementare uno spazio di memoria di 16Mx8bit usando due moduli RAM da 8Mx8bit, in modo che il modulo 1 dia corso alle celle di indirizzo *pari* ed il modulo 2 a quelle di indirizzo *dispari*. I select dei due moduli /s1, /s2 vengono generati da maschere che hanno come ingressi:

- a) a23\_a1

- b) a0

- c) a23

- d) Nessuna delle precedenti

2) Un D-latch viene pilotato con la sequenza di ingressi  $\{d,c\} = \{0,0\}, \{1,0\}, \{0,1\}, \{1,0\}$ . Alla fine, la sua uscita:

- a) Vale 1

- b) Vale 0

- c) Dipende dal valore impostato al reset

- d) Nessuna delle precedenti

$$T \geq T_{\text{prop}} + T_{\text{a valle}}$$

3) La disuguaglianza scritta sopra riguarda:

- a) Il percorso da registro a registro in una rete di Mealy Ritardato

- b) Il percorso da registro a registro in una rete di Moore

- c) Il percorso da registro a uscita in una rete di Mealy

- d) Nessuna delle precedenti

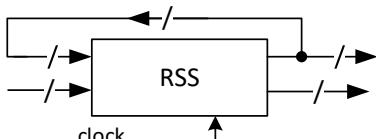

4) L'uscita del circuito in figura può evolversi in modo non prevedibile se la RSS è una rete di:

- a) Moore

- b) Mealy

- c) Mealy ritardato

- d) Nessuna delle precedenti

S0: **begin** ...; STAR<=MJR; **end**

S1: **begin** ...; STAR<=S0; **end**

| St. int. | $\mu$ -code | Ceff | $\mu$ -add T | $\mu$ -add F | $\mu$ -tipo |

|----------|-------------|------|--------------|--------------|-------------|

| S0       | ...         |      |              |              |             |

| S1       | ...         |      |              |              |             |

5) Data la porzione di descrizione e lo schema di ROM riportati sopra, come vanno riempite le quattro colonne di ROM evidenziate a destra?

a)

|   |   |   |   |

|---|---|---|---|

| - | - | - | 1 |

| - | - | - | 0 |

b)

|   |    |    |   |

|---|----|----|---|

| - | -  | -  | 1 |

| - | S0 | S0 | 0 |

c)

|     |    |   |   |

|-----|----|---|---|

| MJR | -  | - | 1 |

| 0   | S0 | - | 0 |

d) Nessuna delle precedenti

```

input a0, a1;

...

casex(STAR)

S0: begin ...; STAR<=(a1,a0)==`B00)?S1:S0; end

S1: begin ...; STAR<=(a1,a0)==`B11)?S0:S1; end

endcase

```

6) Per sintetizzare secondo il modello PO/PC la descrizione sopra riportata, quante uscite ha la rete combinatoria di condizionamento?

- a) 1

- b) 2

- c) Non è possibile stabilirlo

- d) Nessuna delle precedenti

7) Si supponga di voler aggiungere al processore visto a lezione l'istruzione PUSHB indirizzo. Quanti byte verranno letti in memoria in totale durante la fase di fetch?

- a) 7

- b) 5

- c) 4

- d) Nessuna delle precedenti

8) Nel calcolatore visto a lezione, per generare una tensione analogica:

- a) si esegue una OUT ad un opportuno offset

- b) si manda in esecuzione un sottoprogramma che fa ciclare il processore in attesa attiva

- c) si esegue una IN da un opportuno offset

- d) Nessuna delle precedenti

9) Chi scrive nei flag FI ed FO di un'interfaccia con handshake?

- a) Il processore

- b) L'interfaccia

- c) I dispositivi esterni

- d) Nessuna delle precedenti

10) Il numero di bit utili da trasmettere in una singola trasmissione seriale ha un limite superiore dovuto a:

- a) l'overhead dei bit di start e di stop

- b) il fatto che la linea di trasmissione non è un conduttore ideale

- c) l'imprecisione relativa dei clock di trasmettitore e ricevitore.

- d) Nessuna delle precedenti

Cognome e nome: \_\_\_\_\_

Matricola: \_\_\_\_\_

Link al form Google per le risposte (i due link sono equivalenti):

<https://forms.gle/Kr3W3EDx5mPnHAfx6>

<https://tinyurl.com/bdhand6t>

♦ - *quadri*

Barrare una sola risposta per domanda

Il punteggio finale è  $-1 \times (\text{n. di risposte errate} + \text{n. domande lasciate in bianco})$

Usare lo spazio bianco sul retro del foglio per appunti, se serve

1) Si vuole implementare uno spazio di memoria di 16Mx8bit usando due moduli RAM da 8Mx8bit, in modo che il modulo 1 dia corso alle celle di indirizzo *pari* ed il modulo 2 a quelle di indirizzo *dispari*. I select dei due moduli /s1, /s2 vengono generati da maschere che hanno come ingressi:

- a) a23\_a1

- b) a0

- c) a23

- d) Nessuna delle precedenti

2) Un D-latch viene pilotato con la sequenza di ingressi  $\{d,c\} = \{0,0\}, \{1,0\}, \{0,1\}, \{1,0\}$ . Alla fine, la sua uscita:

- a) Vale 1

- b) Vale 0

- c) Dipende dal valore impostato al reset

- d) Nessuna delle precedenti

$$T \geq T_{\text{prop}} + T_{\text{a valle}}$$

3) La disuguaglianza scritta sopra riguarda:

- a) Il percorso da registro a registro in una rete di Mealy Ritardato

- b) Il percorso da registro a registro in una rete di Moore

- c) Il percorso da registro a uscita in una rete di Mealy

- d) Nessuna delle precedenti

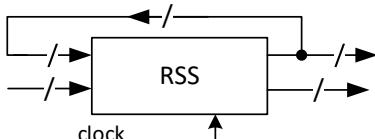

4) L'uscita del circuito in figura può evolversi in modo non prevedibile se la RSS è una rete di:

- a) Moore

- b) Mealy

- c) Mealy ritardato

- d) Nessuna delle precedenti

S0: **begin** ...; STAR<=MJR; **end**

S1: **begin** ...; STAR<=S0; **end**

| St. int. | $\mu$ -code | Ceff | $\mu$ -add T | $\mu$ -add F | $\mu$ -tipo |

|----------|-------------|------|--------------|--------------|-------------|

| S0       | ...         |      |              |              |             |

| S1       | ...         |      |              |              |             |

5) Data la porzione di descrizione e lo schema di ROM riportati sopra, come vanno riempite le quattro colonne di ROM evidenziate a destra?

a)

|   |   |   |   |

|---|---|---|---|

| - | - | - | 1 |

| - | - | - | 0 |

b)

|   |    |    |   |

|---|----|----|---|

| - | -  | -  | 1 |

| - | S0 | S0 | 0 |

c)

|     |    |   |   |

|-----|----|---|---|

| MJR | -  | - | 1 |

| 0   | S0 | - | 0 |

d) Nessuna delle precedenti

```

input a0, a1;

...

casex (STAR)

S0: begin ...; STAR<=(a1,a0)==`B00)?S1:S0; end

S1: begin ...; STAR<=(a1,a0)==`B11)?S0:S1; end

endcase

```

6) Per sintetizzare secondo il modello PO/PC la descrizione sopra riportata, quante uscite ha la rete combinatoria di condizionamento?

- a) 1

- b) 2

- c) Non è possibile stabilirlo

- d) Nessuna delle precedenti

7) Si supponga di voler aggiungere al processore visto a lezione l'istruzione PUSHB indirizzo. Quanti byte verranno letti in memoria in totale durante la fase di fetch?

- a) 7

- b) 5

- c) 4

- d) Nessuna delle precedenti

8) Nel calcolatore visto a lezione, per generare una tensione analogica:

- a) si esegue una OUT ad un opportuno offset

- b) si manda in esecuzione un sottoprogramma che fa ciclare il processore in attesa attiva

- c) si esegue una IN da un opportuno offset

- d) Nessuna delle precedenti

9) Chi scrive nei flag FI ed FO di un'interfaccia con handshake?

- a) Il processore

- b) L'interfaccia

- c) I dispositivi esterni

- d) Nessuna delle precedenti

10) Il numero di bit utili da trasmettere in una singola trasmissione seriale ha un limite superiore dovuto a:

- a) l'overhead dei bit di start e di stop

- b) il fatto che la linea di trasmissione non è un conduttore ideale

- c) l'imprecisione relativa dei clock di trasmettitore e ricevitore.

- d) Nessuna delle precedenti

Cognome e nome: \_\_\_\_\_

Matricola: \_\_\_\_\_

Link al form Google per le risposte (i due link sono equivalenti):

<https://forms.gle/Kr3W3EDx5mPnHAfx6>

<https://tinyurl.com/bdhand6t>

♣ - *fiori*

Barrare una sola risposta per domanda

Il punteggio finale è  $-1 \times (\text{n. di risposte errate} + \text{n. domande lasciate in bianco})$

Usare lo spazio bianco sul retro del foglio per appunti, se serve

1) Si vuole implementare uno spazio di memoria di 16Mx8bit usando due moduli RAM da 8Mx8bit, in modo che il modulo 1 dia corso alle celle di indirizzo *pari* ed il modulo 2 a quelle di indirizzo *dispari*. I select dei due moduli /s1, /s2 vengono generati da maschere che hanno come ingressi:

- a) a23\_a1

- b) a0

- c) a23

- d) Nessuna delle precedenti

2) Un D-latch viene pilotato con la sequenza di ingressi  $\{d,c\} = \{0,0\}, \{1,0\}, \{0,1\}, \{1,0\}$ . Alla fine, la sua uscita:

- a) Vale 1

- b) Vale 0

- c) Dipende dal valore impostato al reset

- d) Nessuna delle precedenti

$$T \geq T_{\text{prop}} + T_{\text{a valle}}$$

3) La disuguaglianza scritta sopra riguarda:

- a) Il percorso da registro a registro in una rete di Mealy Ritardato

- b) Il percorso da registro a registro in una rete di Moore

- c) Il percorso da registro a uscita in una rete di Mealy

- d) Nessuna delle precedenti

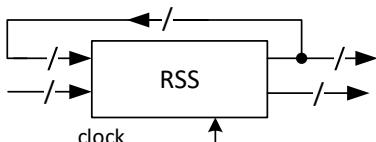

4) L'uscita del circuito in figura può evolversi in modo non prevedibile se la RSS è una rete di:

- a) Moore

- b) Mealy

- c) Mealy ritardato

- d) Nessuna delle precedenti

S0: **begin** ...; STAR<=MJR; **end**

S1: **begin** ...; STAR<=S0; **end**

| St. int. | $\mu$ -code | Ceff | $\mu$ -add T | $\mu$ -add F | $\mu$ -tipo |

|----------|-------------|------|--------------|--------------|-------------|

| S0       | ...         |      |              |              |             |

| S1       | ...         |      |              |              |             |

5) Data la porzione di descrizione e lo schema di ROM riportati sopra, come vanno riempite le quattro colonne di ROM evidenziate a destra?

a)

|   |   |   |   |

|---|---|---|---|

| - | - | - | 1 |

| - | - | - | 0 |

b)

|   |    |    |   |

|---|----|----|---|

| - | -  | -  | 1 |

| - | S0 | S0 | 0 |

c)

|     |    |   |   |

|-----|----|---|---|

| MJR | -  | - | 1 |

| 0   | S0 | - | 0 |

d) Nessuna delle precedenti

```

input a0, a1;

...

casex (STAR)

S0: begin ...; STAR<=({a1,a0}==`B00)?S1:S0; end

S1: begin ...; STAR<=({a1,a0}==`B11)?S0:S1; end

endcase

```

6) Per sintetizzare secondo il modello PO/PC la descrizione sopra riportata, quante uscite ha la rete combinatoria di condizionamento?

- a) 1

- b) 2

- c) Non è possibile stabilirlo

- d) Nessuna delle precedenti

7) Si supponga di voler aggiungere al processore visto a lezione l'istruzione PUSHB indirizzo. Quanti byte verranno letti in memoria in totale durante la fase di fetch?

- a) 7

- b) 5

- c) 4

- d) Nessuna delle precedenti

8) Nel calcolatore visto a lezione, per generare una tensione analogica:

- a) si esegue una OUT ad un opportuno offset

- b) si manda in esecuzione un sottoprogramma che fa ciclare il processore in attesa attiva

- c) si esegue una IN da un opportuno offset

- d) Nessuna delle precedenti

9) Chi scrive nei flag FI ed FO di un'interfaccia con handshake?

- a) Il processore

- b) L'interfaccia

- c) I dispositivi esterni

- d) Nessuna delle precedenti

10) Il numero di bit utili da trasmettere in una singola trasmissione seriale ha un limite superiore dovuto a:

- a) l'overhead dei bit di start e di stop

- b) il fatto che la linea di trasmissione non è un conduttore ideale

- c) l'imprecisione relativa dei clock di trasmettitore e ricevitore.

- d) Nessuna delle precedenti

Cognome e nome: \_\_\_\_\_

Matricola: \_\_\_\_\_

Link al form Google per le risposte (i due link sono equivalenti):

<https://forms.gle/Kr3W3EDx5mPnHAfx6>

<https://tinyurl.com/bdhand6t>

♠ - *picche*